# Semiconductor Technology

from A to Z

www.halbleiter.org

# **Contents**

| Li | st of | Figure | s                                                 | VII |

|----|-------|--------|---------------------------------------------------|-----|

| Li | st of | Tables |                                                   | XI  |

| 1  | Fun   | damen  | ntals                                             | 1   |

|    | 1.1   | The at | tomic structure                                   | 1   |

|    |       | 1.1.1  | The atomic model                                  | 1   |

|    |       | 1.1.2  | Properties of atoms                               | 2   |

|    | 1.2   | The el | lements, the periodic table                       | 3   |

|    |       | 1.2.1  | Elements                                          | 3   |

|    |       | 1.2.2  | The periodic table of the chemical elements       | 3   |

|    | 1.3   | Chem   | iical bonds                                       | 4   |

|    |       | 1.3.1  | Chemical bonds                                    | 4   |

|    |       | 1.3.2  | The atomic bond                                   | 5   |

|    |       | 1.3.3  | The ionic bond                                    | 6   |

|    |       | 1.3.4  | The metallic bonding                              | 6   |

|    |       | 1.3.5  | Intermolecular bondings                           | 7   |

|    | 1.4   | Noble  | e gases                                           | 8   |

|    | 1.5   | Cond   | uctors - Insulators - Semiconductors              | 9   |

|    |       | 1.5.1  | Conductors                                        | 9   |

|    |       | 1.5.2  | Insulators                                        | 10  |

|    |       | 1.5.3  | Semiconductors                                    | 10  |

|    |       | 1.5.4  | The band model                                    | 11  |

|    | 1.6   | Dopir  | ng: n- and p-semiconductors                       | 14  |

|    |       | 1.6.1  | Doping                                            | 14  |

|    |       | 1.6.2  | n-doping                                          | 14  |

|    |       | 1.6.3  | p-doping                                          | 15  |

|    |       | 164    | Electronic hand structure in doned semiconductors | 16  |

|   | 1.7        | The p-   | n junction                                  | 17       |

|---|------------|----------|---------------------------------------------|----------|

|   |            | 1.7.1    | p-n junction at thermal equilibrium         | 17       |

|   |            | 1.7.2    | p-n junction with external applied voltage  | 18       |

|   | 1.8        | Field-   | effect transistors                          | 19       |

|   |            | 1.8.1    | General layout                              | 19       |

|   |            | 1.8.2    | Construction of a n-channel FET             | 20       |

|   |            | 1.8.3    | Mode of operation                           | 25       |

|   | 1.9        | Bipola   | r transistors                               | 26       |

|   |            | 1.9.1    | General layout                              | 26       |

|   |            | 1.9.2    | Construction of an NPN bipolar transistor   | 27       |

|   |            | 1.9.3    | Mode of operation                           | 29       |

|   | 1.10       | Const    | ruction of a FinFET                         | 30       |

|   |            | 1.10.1   | General layout and mode of operation        | 30       |

|   |            | 1.10.2   | Construction of a bulk silicon-based FinFET | 30       |

| 2 | Waf        | er fabri | ication                                     | 33       |

| _ | 2.1        |          | rties of silicon                            | 33       |

|   | 2.1        | -        | ilicon                                      | 34       |

|   | 2.2        | 2.2.1    | Production of raw silicon                   | 34       |

|   |            | 2.2.1    | Purification of the raw silicon             | 34       |

|   |            | 2.2.3    | Zone cleaning                               | 35       |

|   | 2.3        |          | ation of the single crystal                 | 36       |

|   | 2.3        | 2.3.1    | The single crystal                          | 36       |

|   |            | 2.3.1    | •                                           | 36       |

|   |            | 2.3.3    | Czochralski process                         | 38       |

|   | 2.4        |          | fabrication                                 | 38       |

|   | <b>4.4</b> | 2.4.1    | Wafer separation and surface refinement     | 38       |

|   |            |          | 1                                           |          |

|   | 2.5        | 2.4.2    | Historical development of the wafer size    | 40       |

|   | 2.5        | •        | g techniques                                | 41       |

|   |            | 2.5.1    | Definition                                  | 41<br>42 |

|   |            | 2.5.2    | Diffusion methods                           |          |

|   |            | 2.5.3    | Diffusion methods                           | 43       |

|   |            | 2.5.4    | Ion implantation                            | 44       |

| 3 | Oxi | dation    |                                                | 48        |

|---|-----|-----------|------------------------------------------------|-----------|

|   | 3.1 | Overv     | view                                           | 48        |

|   |     | 3.1.1     | Application                                    | 48        |

|   |     | 3.1.2     | Properties of oxide layers                     | 48        |

|   | 3.2 | Fabric    | cation of oxide layers                         | 49        |

|   |     | 3.2.1     | Thermal oxidation                              | 49        |

|   |     | 3.2.2     | Oxidation by vapor deposition                  | 52        |

|   | 3.3 | LOCC      | OS process                                     | 53        |

|   |     | 3.3.1     | Very large-scale integration                   | 53        |

|   |     | 3.3.2     | Bird's beak                                    | 53        |

|   |     | 3.3.3     | Alternative                                    | 55        |

|   | 3.4 | Film t    | hickness measurement                           | 55        |

|   |     | 3.4.1     | Metrology                                      | 55        |

|   |     | 3.4.2     | Interferometry                                 | 56        |

|   |     | 3.4.3     | Ellipsometry                                   | 57        |

|   |     | 3.4.4     | Appraisal of the measurement                   | 58        |

| 4 | Den | osition   | 1                                              | 59        |

| 7 | 4.1 |           |                                                | <b>59</b> |

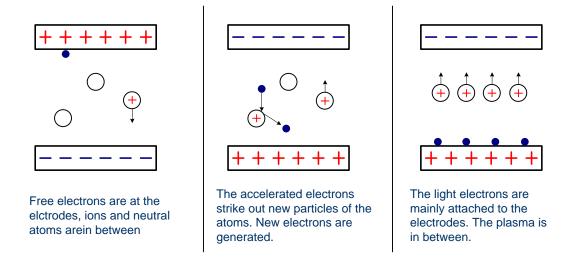

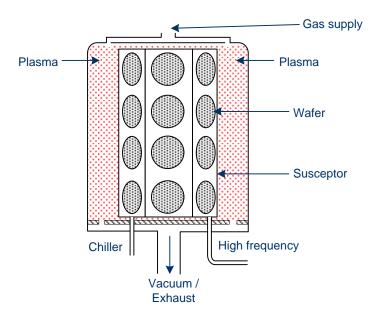

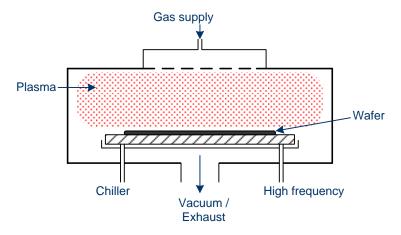

|   | 4.1 | 4.1.1     | na, the fourth aggregation state of a material | 59        |

|   |     | 4.1.1     | Plasma generation                              | 60        |

|   | 4.2 |           | ical vapor deposition                          | 61        |

|   | 4.4 | 4.2.1     | Silicon vapor phase epitaxy                    | 61        |

|   |     | 4.2.1     | CVD process: Chemical Vapor Deposition         | 63        |

|   |     | 4.2.3     | APCVD: Atmospheric Pressure CVD                | 64        |

|   |     | 4.2.4     | LPCVD: Low Pressure CVD                        | 65        |

|   |     | 4.2.5     | PECVD: Plasma Enhanced CVD                     | 66        |

|   |     | 4.2.6     | ALD: Atomic Layer Deposition                   | 67        |

|   | 4.3 |           | cal deposition methods                         | 69        |

|   | 1.0 | 4.3.1     | Molecular beam epitaxy                         | 69        |

|   |     | 4.3.2     | Evaporating                                    | 69        |

|   |     | 4.3.3     | Sputtering                                     | 70        |

|   |     |           | o                                              | - 3       |

| 5 |     | allizatio |                                                | 73        |

|   | 5.1 | Requi     | rements on metallization                       | 73        |

|   | 5.2 | Alum    | inum technology               | 74  |

|---|-----|---------|-------------------------------|-----|

|   |     | 5.2.1   | Aluminum and aluminum alloy   | 74  |

|   |     | 5.2.2   | Diffusion in silicon          | 74  |

|   |     | 5.2.3   | Electromigration              | 75  |

|   |     | 5.2.4   | Hillocks                      | 76  |

|   | 5.3 | Coppe   | er technology                 | 76  |

|   |     | 5.3.1   | Copper technology             | 76  |

|   |     | 5.3.2   | Damascene process             | 77  |

|   |     | 5.3.3   | Low-k technology              | 81  |

|   | 5.4 | Metal   | semiconductor junction        | 84  |

|   |     | 5.4.1   | Metal semiconductor junction  | 84  |

|   |     | 5.4.2   | Band model of p-n junctions   | 87  |

|   | 5.5 | Wiring  | g                             | 88  |

|   |     | 5.5.1   | Wiring                        | 88  |

|   |     | 5.5.2   | BPSG reflow                   | 88  |

|   |     | 5.5.3   | Reflow back etching           | 88  |

|   |     | 5.5.4   | Chemical mechanical polishing | 89  |

|   |     | 5.5.5   | Contacting                    | 90  |

| 6 | Pho | tolitho | graphie                       | 91  |

| • | 6.1 |         | 3 · F ·                       | 91  |

|   | 0.1 | 6.1.1   | 8                             | 91  |

|   |     | 6.1.2   |                               | 91  |

|   |     | 6.1.3   |                               | 92  |

|   |     | 6.1.4   | -                             | 93  |

|   |     | 6.1.5   | •                             | 94  |

|   | 6.2 | Expos   |                               | 95  |

|   |     | 6.2.1   |                               | 95  |

|   |     | 6.2.2   |                               | 95  |

|   |     | 6.2.3   | 1                             | 95  |

|   |     | 6.2.4   |                               | 96  |

|   |     | 6.2.5   | ·                             | 98  |

|   |     | 6.2.6   | 0 1 7                         | 99  |

|   |     | 6.2.7   |                               | 99  |

|   | 6.3 | Photo   |                               | .00 |

|   | 0.5 | 111000  | 1CD1Dt                        | UU  |

|   |     | 6.3.2   | Chemical composition                    |

|---|-----|---------|-----------------------------------------|

|   | 6.4 | Develo  | opment and inspection                   |

|   |     | 6.4.1   | Development                             |

|   |     | 6.4.2   | Inspection                              |

|   |     | 6.4.3   | Resist removal                          |

|   | 6.5 | Photo   | masks                                   |

|   |     | 6.5.1   | Introduction                            |

|   |     | 6.5.2   | Photomask manufacture                   |

|   |     | 6.5.3   | Photomasks                              |

|   |     | 6.5.4   | Next generation lithography             |

| 7 | Wet | chemi   | stry 110                                |

|   | 7.1 | Etch p  | rocesses                                |

|   | 7.2 | Wet et  | ching                                   |

|   |     | 7.2.1   | Principle                               |

|   |     | 7.2.2   | Requirements                            |

|   |     | 7.2.3   | Batch etching                           |

|   |     | 7.2.4   | Spray etching                           |

|   |     | 7.2.5   | Anisotropic etching of silicon          |

|   |     | 7.2.6   | Etching solutions for isotropic etching |

|   | 7.3 | Wafer   | cleaning                                |

|   |     | 7.3.1   | Cleanroom                               |

|   |     | 7.3.2   | Types of contamination                  |

|   |     | 7.3.3   | Microscopic contamination               |

|   |     | 7.3.4   | Molecular contamination                 |

|   |     | 7.3.5   | Alkaline and metallic contamination     |

|   |     | 7.3.6   | Cleaning techniques                     |

| 8 | Dry | etching | g 121                                   |

|   | 8.1 | Overv   | iew                                     |

|   |     | 8.1.1   | Abstract                                |

|   |     | 8.1.2   | Major values in dry etching             |

|   |     | 8.1.3   | Dry etch processes                      |

|   | 8.2 | Dry et  | ch processes                            |

|   |     | 8.2.1   | Ion Beam Etching                        |

|   |     | 8.2.2   | Plasma Etching                          |

| 8.2.3 | Reactive Ion Etching |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 125 |

|-------|----------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

|       |                      | - | - | - | - | - | - | • | - | • | - | - | - | - | - | - | - | - | - | - | - | - | - | • | - | - | - |     |

# **List of Figures**

| 1.1                    | Simplified illustration of a neon atom                                 | 1   |

|------------------------|------------------------------------------------------------------------|-----|

| 1.2                    | Elementary particles                                                   | 2   |

| 1.3                    | Important elements in semiconductor industry                           | 2   |

| 1.4                    | The periodic table of the elements                                     | 4   |

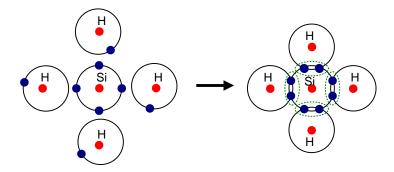

| 1.5                    | The atomic bond of silane                                              | 6   |

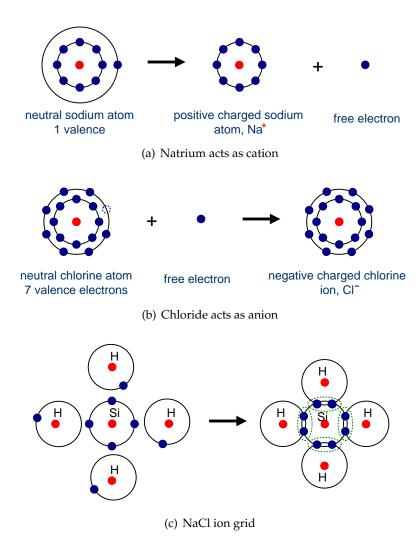

| 1.6                    | Principle of the ion bounding                                          | 7   |

| 1.7                    | Metallic bonding                                                       | 8   |

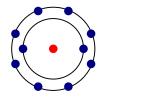

| 1.8                    | Noble gases                                                            | 9   |

| 1.9                    | Metallic bonding: fixed ions and free valence electrons (Fermi gas)    | 10  |

| 1.10                   | Cut-out of a silicon lattice                                           | 11  |

| 1.11                   | Energy levels of atoms which are in interdependency with other atoms . | 12  |

| 1.12                   | Energy bands of atoms which are in interdependency with other atoms .  | 12  |

| 1.13                   | The band model                                                         | 14  |

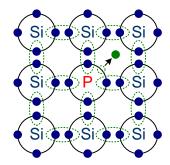

| 1.14                   | n-doping with phosphorus                                               | 15  |

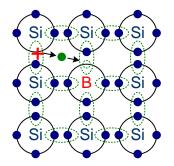

| 1.15                   | p-doping with boron                                                    | 16  |

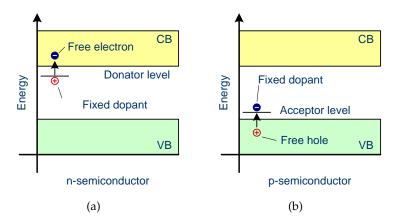

| 1.16                   | Band model of p- and n-type doped semiconductors                       | 17  |

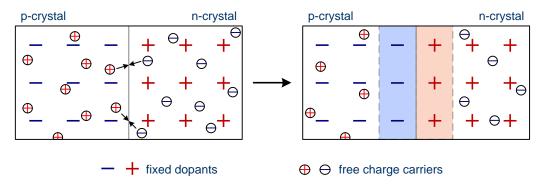

| 1.17                   | p-n junction without an external applied voltage                       | 18  |

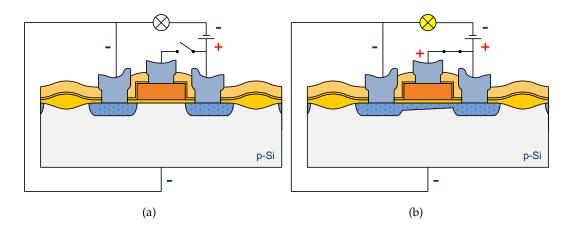

| 1.18                   | p-n junction with an external applied voltage                          | 19  |

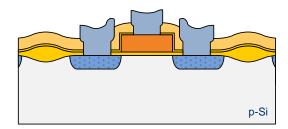

| 1.19                   | Enhancement nFET                                                       | 26  |

| 1.20                   | SBC bipolar transistor                                                 | 29  |

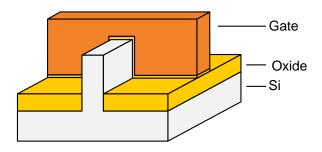

| 1.21                   | FinFET in bulk process                                                 | 32  |

| 1.22                   | FinFET on SOI                                                          | 32  |

| 2.1                    | Illustration of the zone cleaning process                              | 35  |

| 2.2                    | Crystal orientation                                                    | 36  |

| 2.3                    | Illustration of the Czochralski and the float-zone process             | 37  |

| 2.3<br>2.4             | •                                                                      | 39  |

| 2. <del>4</del><br>2.5 | Different types of wafers                                              | 39  |

| / h                    | Anniliar and wire saw                                                  | -34 |

| 2.6  | Beveling                                                               | 40         |

|------|------------------------------------------------------------------------|------------|

| 2.7  | Different wafer sizes                                                  | 41         |

| 2.8  | Diffusion process                                                      | 43         |

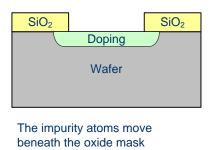

| 2.9  | Diffusion with an oxide mask                                           | 44         |

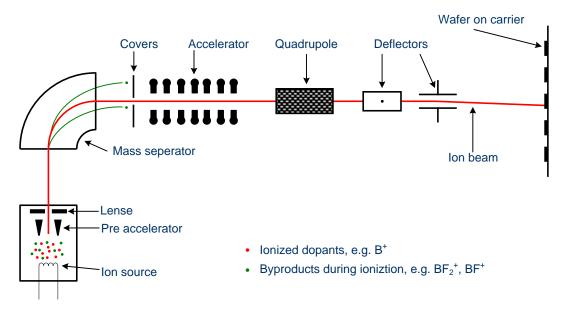

| 2.10 | Illustration of an ion implanter                                       | 45         |

| 2.11 | Channeling effect in the ingot                                         | 46         |

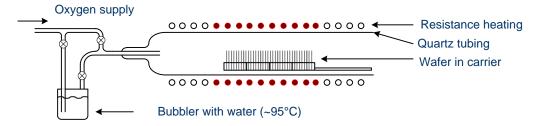

| 3.1  | Illustration of a furnace for therma oxidation                         | 49         |

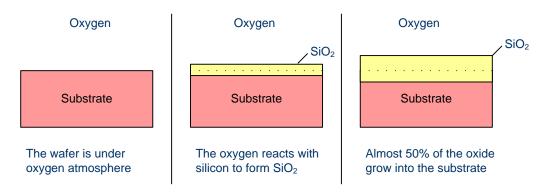

| 3.2  | Growth of silicon dioxide on top of silicon                            | 52         |

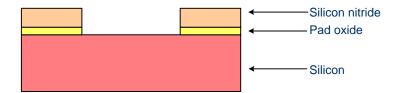

| 3.3  | Basic film layer stack                                                 | 54         |

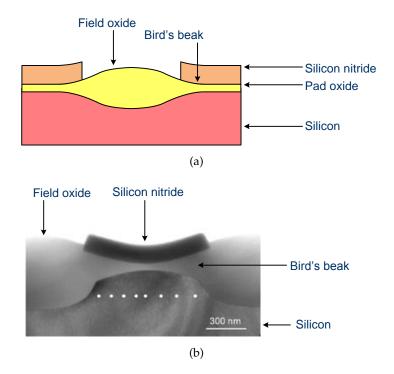

| 3.4  | LOCOS profile after oxidation                                          | 54         |

| 3.5  | Example of the LOCOS process for lateral isolation of transistors      | 55         |

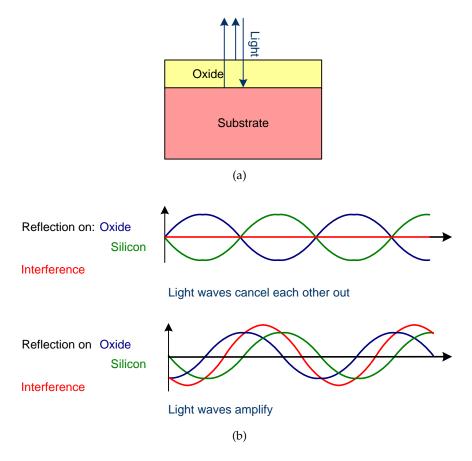

| 3.6  | Interferometry, destructive and constructive superimposition of light- |            |

|      | waves                                                                  | 56         |

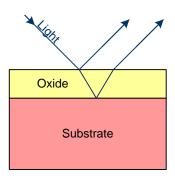

| 3.7  | Ellipsometry                                                           | 57         |

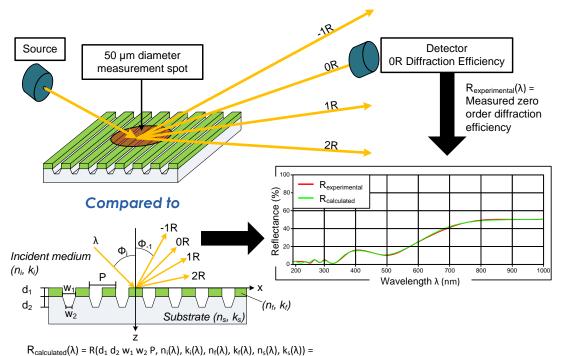

| 3.8  | Simulated and real measurement                                         | 58         |

| 4.1  | Illustration of plasma generation                                      | 61         |

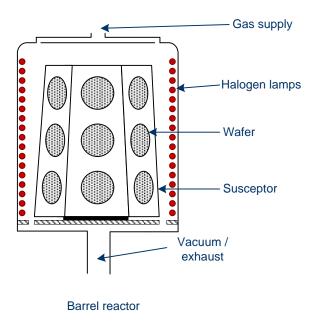

| 4.2  | Illustration of a barrel reactor for epitactical processes             | 63         |

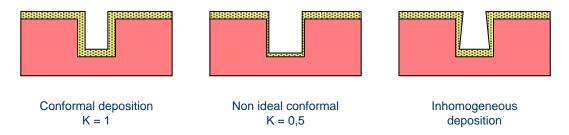

| 4.3  | Deposition profiles with different conformity                          | 64         |

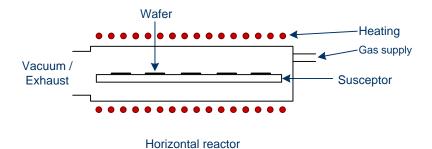

| 4.4  | Illustration of a horizontal APCVD reactor                             | 65         |

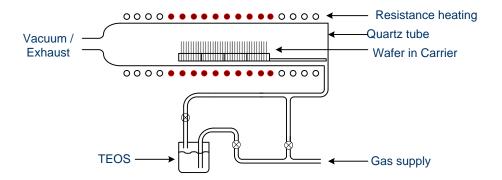

| 4.5  | Illustration of a LPCVD reactor for TEOS films                         | 66         |

| 4.6  | Illustration of a PECVD reactor                                        | 66         |

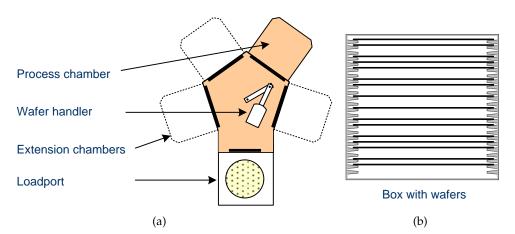

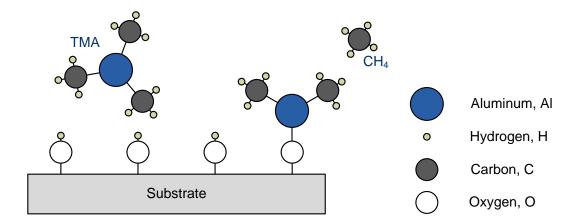

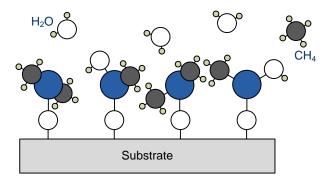

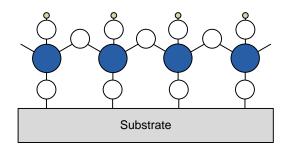

| 4.7  | Introduction of TMA into the process chamber                           | 67         |

| 4.8  | Adhesion of TMA at the surface atoms                                   | 68         |

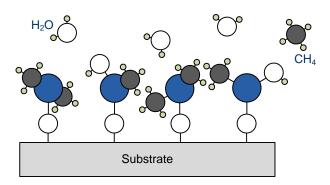

| 4.9  | Introduction of water into the process chamber                         | 68         |

| 4.10 | Saturated surface at the end of one cycle                              | 69         |

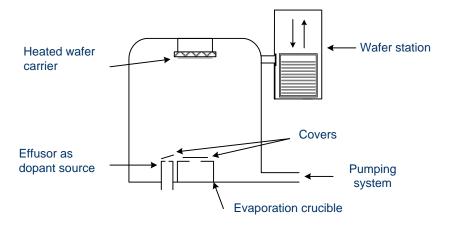

| 4.11 | Illustration of a MBE chamber                                          | 70         |

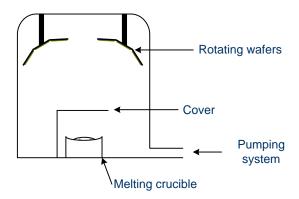

| 4.12 | Illustration of an evaporating chamber                                 | 70         |

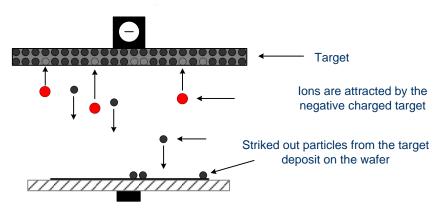

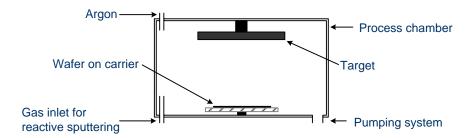

| 4.13 | Illustration of the sputter process                                    | 71         |

| 4.14 | Illustration of a sputter chamber                                      | 72         |

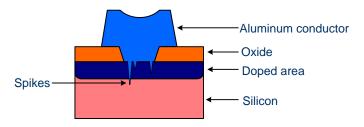

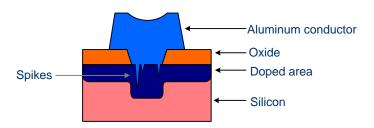

| 5.1  | Spikes                                                                 | 74         |

| 5.2  | Contact implantation                                                   | <b>7</b> 5 |

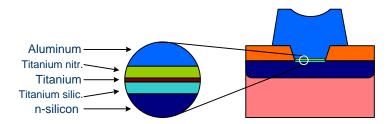

| 5.3  | Barrier layer between aluminum and silicon                             | <b>7</b> 5 |

| 5.4  | Edge rounding                                                          | 76         |

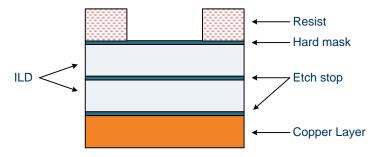

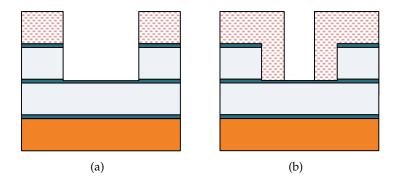

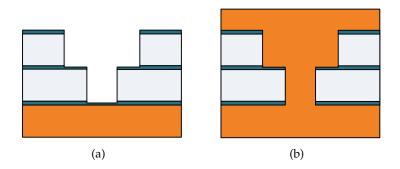

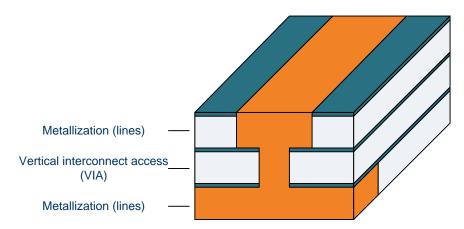

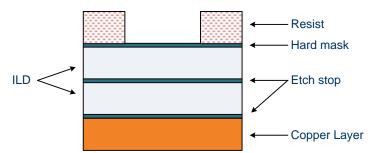

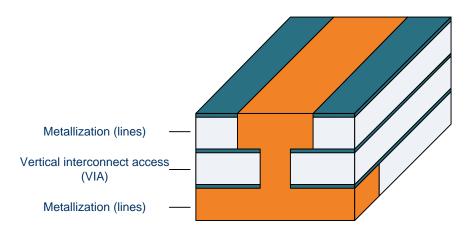

| 5.5  | Basic film stack of a damascene approach                               | 78         |

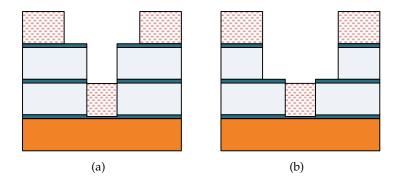

| 5.6  | Trench etch and via resist mask                                                         |

|------|-----------------------------------------------------------------------------------------|

| 5.7  | Final structure after etch and copper deposition                                        |

| 5.8  | Damascene stack after metallization and CMP                                             |

| 5.9  | Damascene stack after VIA etch                                                          |

| 5.10 | Photolithography and trench etch                                                        |

| 5.11 | Damascene stack after metallization and CMP                                             |

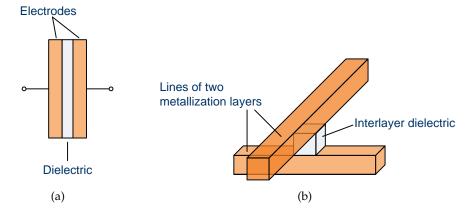

| 5.12 | Traditional capacitor and crossing of two conductors 8                                  |

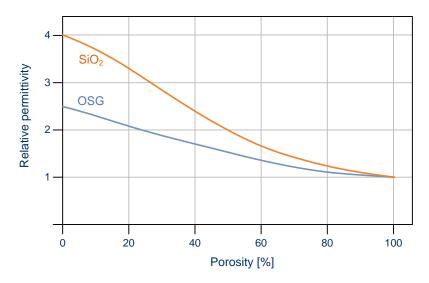

| 5.13 | Relative static permittivity against porosity                                           |

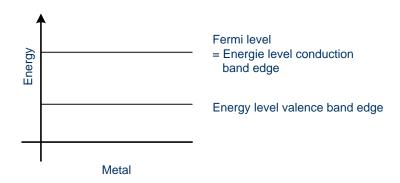

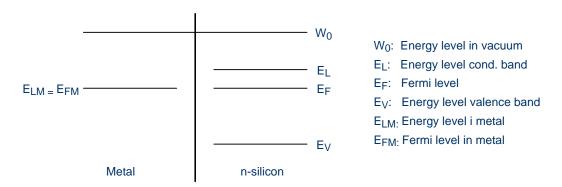

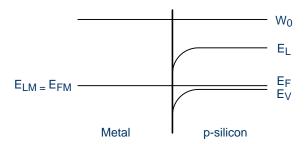

| 5.14 | Fermi level in metals                                                                   |

| 5.15 | Fermi level in doped semiconductors                                                     |

| 5.16 | Band model before the contact                                                           |

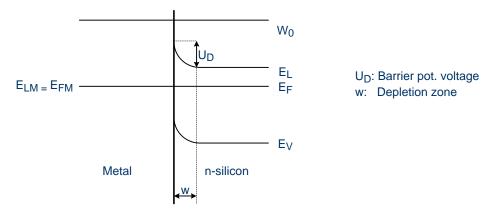

| 5.17 | Band model after the contact                                                            |

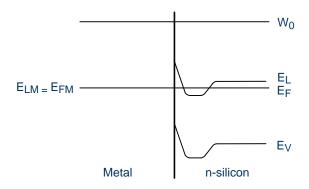

| 5.18 | Band model after $n^+$ -doping                                                          |

| 5.19 | Band model after the contact of metal and p-semiconductors 8                            |

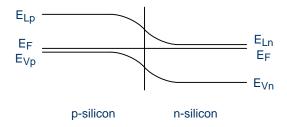

| 5.20 | Band model at the interface of n- and p-doped semiconductors 8                          |

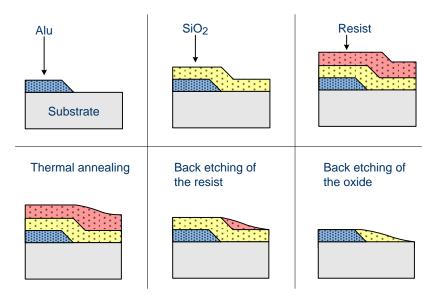

| 5.21 | Reflow back etching process                                                             |

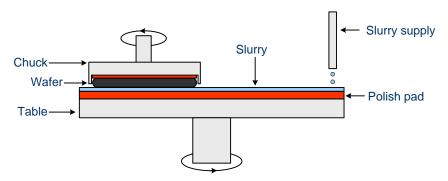

| 5.22 | Illustration of a polisher                                                              |

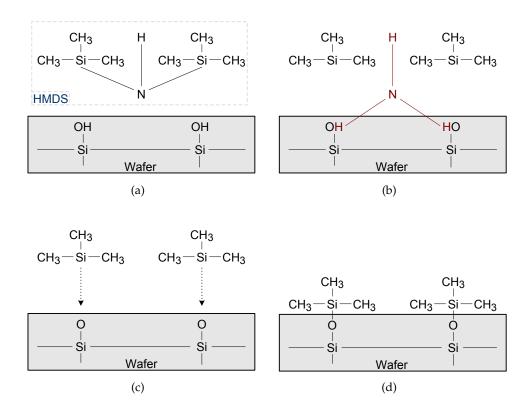

| 6.1  | Surface modifictation with HMDS                                                         |

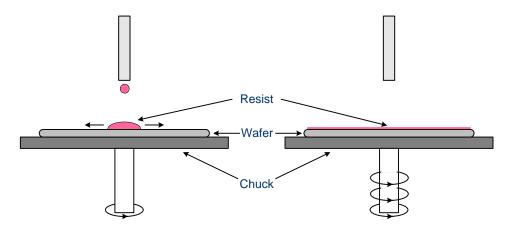

| 6.2  | Spin on coating                                                                         |

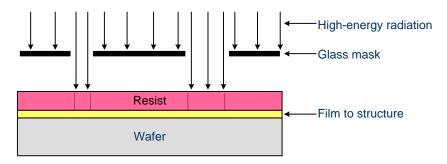

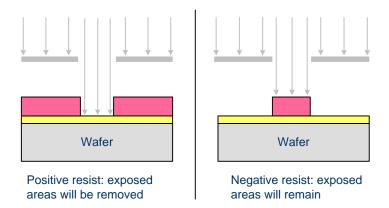

| 6.3  |                                                                                         |

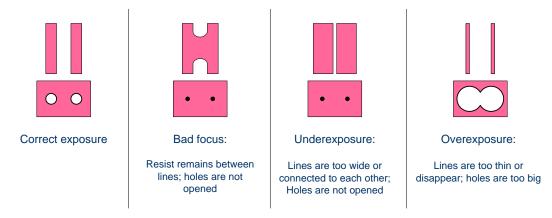

| 6.4  |                                                                                         |

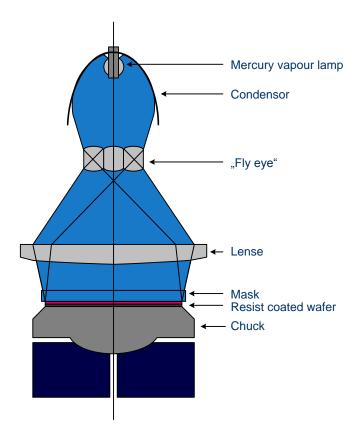

| 6.5  | Bad exposure due to focus issues, over exposure, or under exposure 94  Contact exposure |

| 6.6  |                                                                                         |

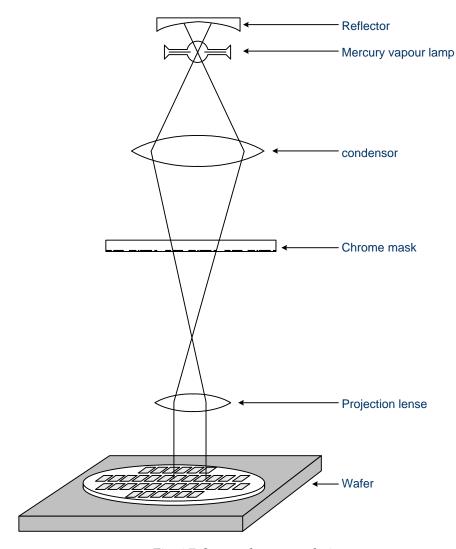

| 6.7  | Proximity exposure                                                                      |

| 6.8  | 1 1                                                                                     |

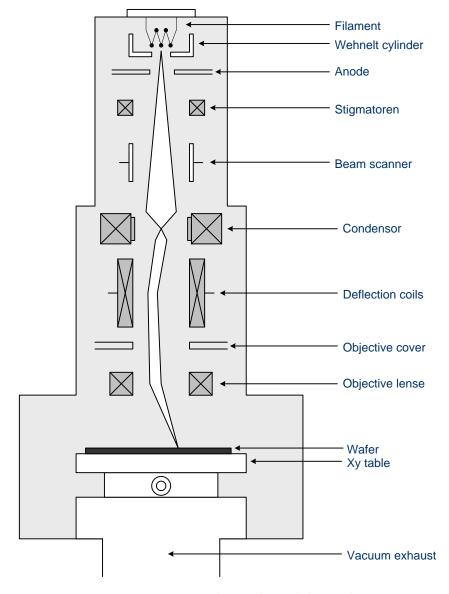

| 6.9  | 0 1 7                                                                                   |

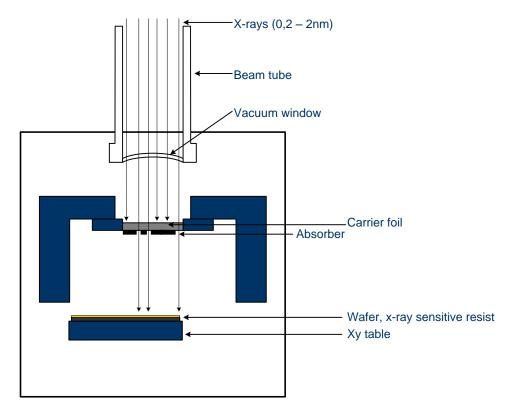

|      | X-ray lithography                                                                       |

|      |                                                                                         |

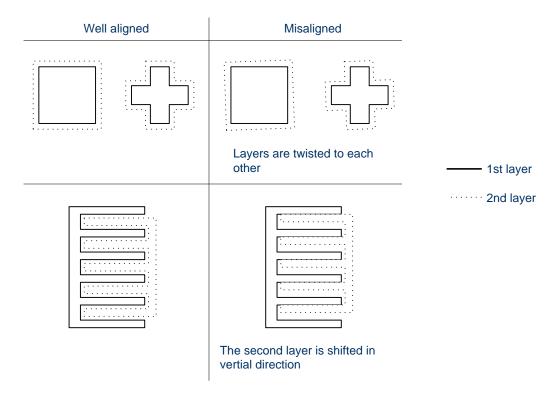

|      | Illustration of alignment marks                                                         |

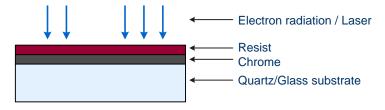

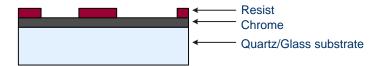

|      | Basic film stack of a chrome on glass mask (COG)                                        |

|      | Development of the resist layer                                                         |

|      | Chrome etch                                                                             |

|      | Resist strip                                                                            |

| 6 16 | A., 1 1 11:1                                                                            |

|      | Attached pellicle                                                                       |

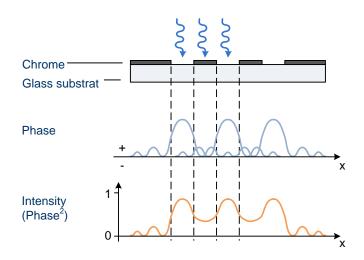

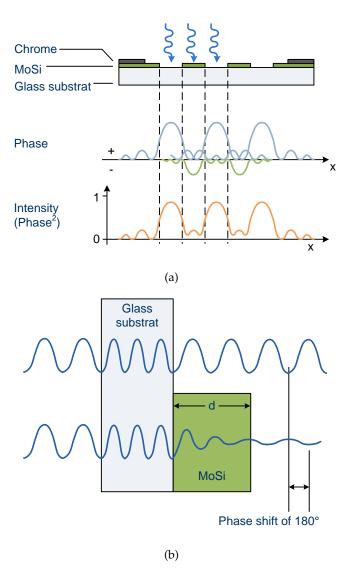

| 6.18 | Spectral intensity of an Attenuated phase shift mask, principle of the |     |

|------|------------------------------------------------------------------------|-----|

|      | phase shift                                                            | 107 |

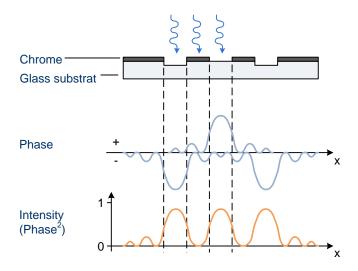

| 6.19 | Spectral intensity of an Alternating Phase Shift Mask                  | 108 |

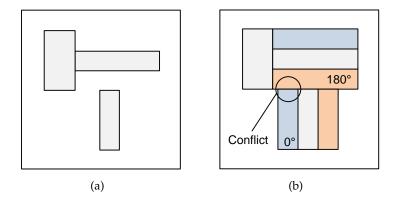

| 6.20 | Desired structures on the wafer and conflict on the mask               | 108 |

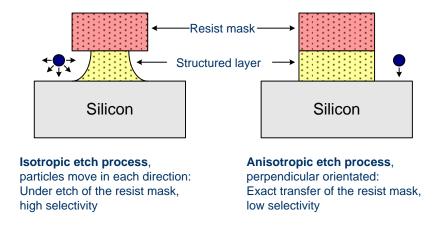

| 7.1  | Isotropic and anisotropic etch processes                               | 110 |

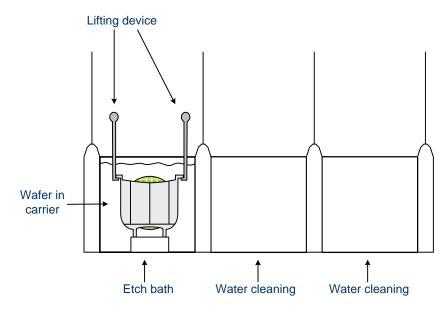

| 7.2  | Batch etching                                                          | 112 |

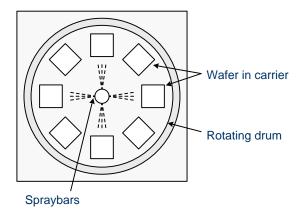

| 7.3  | Spray etching                                                          | 113 |

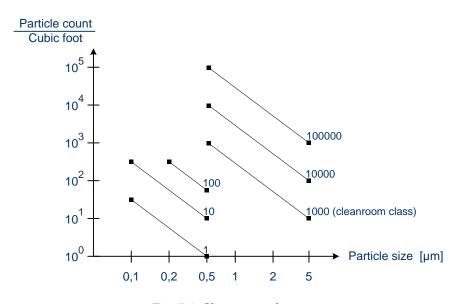

| 7.4  | Cleanroom classes                                                      | 115 |

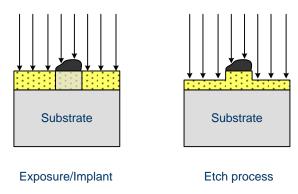

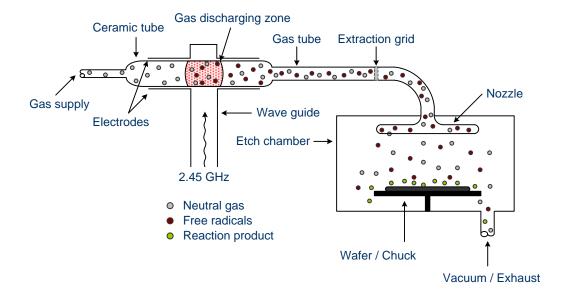

| 7.5  | Shadowing in etch and ion implant processes due to particles           | 117 |

| 7.6  | Embedded particle                                                      | 117 |

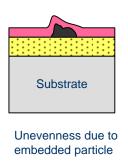

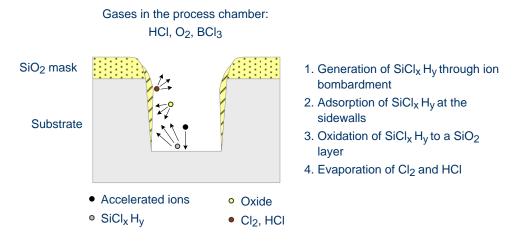

| 8.1  | Illustrationn of an ion beam etch reactor                              | 123 |

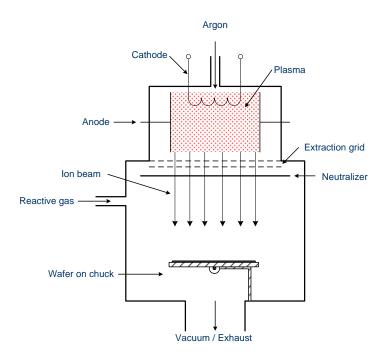

| 8.2  | Illustration of a CDE reactor                                          | 124 |

| 8.3  | Generation process of radicals                                         | 124 |

| 8.4  | Illustration of a RIE reactor in hexagonal construction                | 126 |

| 8.5  | Illustration of a RIE reactor                                          | 127 |

| 8.6  | Sidewall passivation during RIE etching                                | 127 |

## **List of Tables**

| 1.1 | Important elements in semiconductor industry                      | 5   |

|-----|-------------------------------------------------------------------|-----|

| 2.1 | Typical data of wafers                                            | 41  |

| 3.1 | Comparison of the growth rate of wet and dry oxidation of silicon | 50  |

| 5.1 | Overview of organic silicon oxides                                | 83  |

| 8.1 | Overview of process gasses used in dry etch processes             | 128 |

## 1 Fundamentals

#### 1.1 The atomic structure

#### 1.1.1 The atomic model

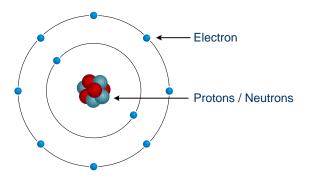

An atom is the smallest chemically not further divisible component of matter. Depending on the atom, it is composed of a certain number of electrons, protons, and neutrons. The positively charged protons and the neutrons form the nucleus, which is encircled by the electrons in certain intervals. A naturally occurring atom is electrically neutral, there are just as many positive protons as negatively charged electrons inside an atom. While the number of neutrons can vary. The simplest atom is the hydrogen atom, with only one electron, one proton, and no neutron. The next heavier atom, the noble gas helium, consists of two electrons, two protons, and two neutrons.

According to the Bohr model of the atom the electrons are assigned to so-called shells, which represent different energy levels and therefore are arranged concentrically to the nucleus. There is a maximum of seven shells, which can hold a different number of electrons, the electrons assigned to the outermost shell are known as valence electrons.

Fig. 1.1: Simplified illustration of a neon atom

The efforts of all the atoms is to fulfill their outermost shell, with eight electrons they reach the so-called noble gas configuration (also electron octet). Elements with few

outer electrons can donate electrons, elements with many outer electrons can accept additional valence electrons (see chapter chemical bonds for details).

#### 1.1.2 Properties of atoms

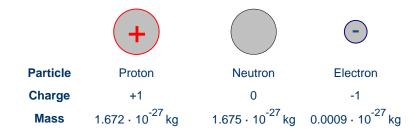

**Mass:** The mass of an atom is determined mainly from the nucleus, since the masses of protons and neutrons  $(1.67 \cdot 10^{-27} \text{ kg})$  are about 1800 times larger than the mass of the electrons in the atomic shell  $(9.11 \cdot 10^{-31} \text{ kg})$ .

**Dimensions:** The diameter of the atomic shell is 0.1 to 0.5 nm, the diameter of the nucleus is even lower by a factor of 100,000. To illustrate: when a pinhead in the middle of a soccer field represents the atomic nucleus, the distance to the corner flags corresponds to the distance at which the electrons orbiting the nucleus.

**Density:** In the nucleus of an atom protons and neutrons are packed extremely densely. If one were to compress the earth to the same density, its radius would be reduce from 6,700,000 m initially to only 100 meters.

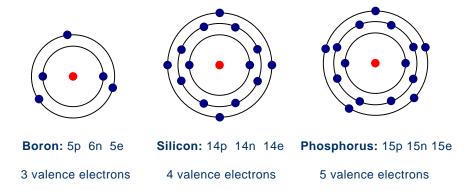

Fig. 1.2: Elementary particles

Fig. 1.3: Important elements in semiconductor industry

### 1.2 The elements, the periodic table

#### 1.2.1 Elements

An element consists of several identical atoms and is a substance that can not be further decomposed by chemical means. The mass of elements is determined only by the number of protons and neutrons, since the electron mass is negligible. Hydrogen with one proton and no neutron has the mass number 1, the next heavier element, helium, has the mass number 4 (2 protons + 2 neutrons).

The elements are usually named with the initials of their Latin or Greek names (from latin hydrogenium: hydrogen H, from greek lithos: lithium Li).

#### 1.2.2 The periodic table of the chemical elements

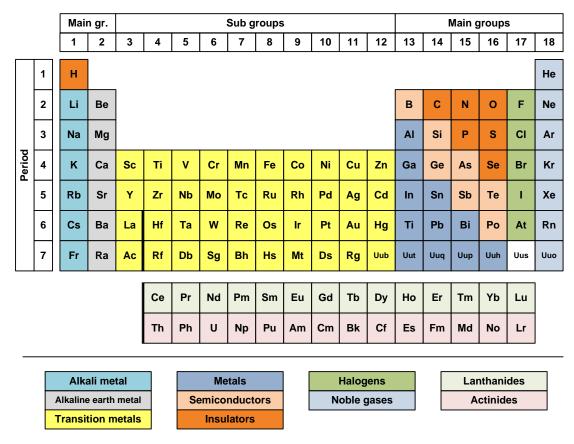

The periodic table of the chemical elements (periodic table) lists all the chemical elements with increasing proton number (atomic number) and according to their chemical properties, divided into periods as well as main and subgroups.

The period represents the number of electron shells, the main group, the number of electrons in the outermost shell (1 to 8 electrons). Group 1 and 2 and 13-18 are the maingroups, the group of 3-12 the subgroups.

The first element with one shell (period 1) and one outer electron (group 1) is hydrogen H. The next element, helium He, has only one electron shell and is therefore in period 1 as well. Since the first shell is completely filled with only two electrons, helium is not in group 2, but in group 18 (group of the noble gases).

To add more electrons, one needs to begin a new electron shell. Thus we find lithium Li in group 1, period 2 (two electrons on the first shell, one valence electron on the second shell). A shell can hold a maximum of  $2n^2$  electrons, where n stands for the period.

From the fourth period there exist the groups (3-12) of the transition elements. After the first two valence electrons were added in maingroup 1 and 2 to the outermost shell, more inner shells are filled in the transitional groups for energetic reasons, before the outer shell is completely filled with electrons in maingroup 13-18.

Elements that occur on the left side in the periodic table are metals. These elements have an aspiration to donate valence electrons to achieve the noble gas configuration.

Fig. 1.4: The periodic table of the elements

On the right side there are the nonmetals, which are trying to accept additional electrons to achieve the noble gas configuration. In between there are the semimetals such as silicon and germanium.

#### 1.3 Chemical bonds

#### 1.3.1 Chemical bonds

Electrons located on the outermost shell, can escape from their atoms by supplying energy (e.g. in the form of heat) and be exchanged with other atoms. Compounds of several atoms are called molecules. The reason for the bond effort is the so-called noble gas configuration - a fulfilled valence shell - which represents an energetically stable state. Substances which have reached a full outer shell, will not form bonds (a few exceptions such as xenon-fluorine compounds are possible).

| Element           | Particle      | Characteristic, application                                                                    |

|-------------------|---------------|------------------------------------------------------------------------------------------------|

| <b>B</b> Boron    | 5p, 6n, 5e    | 3 valence electrons: used for p-doping of silicon                                              |

| <b>N</b> Nitrogen | 7p, 7n, 7e    | Stable $N_2$ molecule: inert gas, cover layer on top of the wafer                              |

| O Oxygen          | 8p, 8n, 8e    | Very reactive: oxidation of silicon, insulating layers (SiO <sub>2</sub> )                     |

| <b>F</b> Fluorine | 9p, 10n, 10e  | Most reactive element: used for etching in combination with other elements (ie $HF$ , $CF_4$ ) |

| Si Silicon        | 14p, 14n, 14e | Bulk material in semiconductor industry                                                        |

| P Phosphorous     | 15p, 16n, 15e | 5 valence electrons: used for n-doping of silicon                                              |

Tab. 1.1: Important elements in semiconductor industry

There are mainly three different types of bonds, which are discussed below.

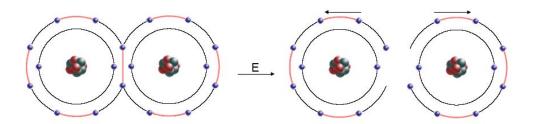

#### 1.3.2 The atomic bond

Nonmetals form this bond to achieve an octet of electrons. For example two fluorine atoms (each with seven outer electrons) can fill their octet of electrons by mutual exchange of one electron. The distance between the two nuclei represents a compromise between the attraction of the nuclei and the bonding electrons and the repulsion of the two nuclei and the electrons as well. The reason for the atomic bond is that nature is always striving to reach the lowest energy state. Since the electrons have more space through the bond of several atoms, which corresponds to a lower energy, the atomic bond is formed.

Since atoms try to achieve the fulfilled outer shell, elemental fluorine atoms never appear as a single atom, but always as a fluorine molecule  $F_2$ . Also nitrogen  $N_2$ , oxygen  $O_2$ , chlorine  $Cl_2$ , bromine  $Br_2$ , and iodine  $I_2$ . The atomic bond also is called covalent bond.

Illustration of the atomic bond of silane ( $SiH_4$ , for silicon only the outermost shell is drawn). The silicon atom reaches the full outermost shell, the hydrogen atoms reach the filled first shell with only two electrons.

Fig. 1.5: The atomic bond of silane

#### 1.3.3 The ionic bond

Ionic bonds are formed by the fusion of metals and nonmetals. While metals donate electrons to achieve a completely filled outer shell, nonmetals accept additional electrons. An example of an ionic bond is NaCl, sodium chloride.

The sodium atom gives off its valence electron (so it has more protons than electrons and is positively charged), while chlorine accepts one electron and thus is negatively charged. Due to the different charges the two atoms attract each other. A charged atom is known as an ion, while a positive ion is called cation and a negative ion anion, respectivley.

Since atoms always occur at a very large number, they form grids due to the attraction and repulsion forces from ions. Substances which form such a grid in solid state, are known as salts.

#### 1.3.4 The metallic bonding

Metals are forming that bond to attain the stable noble gas configuration. Each metal atom gives off its outer electrons: thus positively charged metal ions and free electrons are genereted with strong attractive forces in between. The metal ions repel each other as well as the electrons.

Since the attraction and repulsion forces act in all dimensions of space, the atoms arrange themselves in a regular lattice. The free electrons are the so-called Fermi gas, which holds the positive metal ions together. Due to the free electrons, metal's electric conductivity is excellent.

Fig. 1.6: Principle of the ion bounding

The physical and chemical properties of compounds are dependent on the type of bonding. Thus greater attraction forces mean higher melting and boiling points, the number of free electrons affects the conductivity.

#### 1.3.5 Intermolecular bondings

Intermolecular bondings differ from chemical bondings in that way that these are only forces between two ore more molucules, ions or atoms. Intermolecular bonds are caused mainly by load displacement which result in attracting or repulsing of particles.

# Free electrons form an electron gas Al<sup>3+</sup> Al<sup>3+</sup>

Fixed aluminum atoms

Fig. 1.7: Metallic bonding

The strongest of these forces is the hydrogen bond. Due to its bonding angle the loads inside a water molecule (H–O–H) are distributed asymmetrical, so that the oxygen atom has a negative partial charge while the hydrogen atoms have a positive partial charge. This load displacement leads to attracting and repulsing of other water molecules. Besides the hydrogen bond there are even weaker forces like the van der Waals interaction.

The bond energy of the chemical bonds is in the range of several hundreds to several thousands kilojoule/mol (kJ/mol). The bond energy of hydrogen bonds is up to a hundred kJ/mol and the bond energy of van der Waals forces is in the range of 0.5 to 5 kJ/mol.

## 1.4 Noble gases

Noble gases are the elements in the eighth maingroup of the periodic table: helium, neon, argon, krypton, xenon, radon (top down).

The specificity of these elements is that they have eight electrons in their outer shell. This octet represents a very stable energetic state, which all elements would like to achieve. In the chapter chemical bonds it is explaind how the elements reach a full outer shell. Due to the stable state of the noble gas configuration, these elements will not go into reaction with other elements (a few xenon-fluorine compounds and others are known).

Neon consists of ten electrons: two on the first shell and eight valence electrons on the

second/outer most shell. Exception: helium, which consists of only one shell, reaches the noble gas configuration already with two electrons (electron duet instead of octet).

Helium: 2 valence electrons on the 1st shell

Fig. 1.8: Noble gases

As inert gases [lat. inert: inactive, neutral] oxygen (eg as purge gas), argon (sputtering), and others are used in the semiconductors industry.

#### 1.5 Conductors - Insulators - Semiconductors

#### 1.5.1 Conductors

Conductors are generally substances which have the property to pass different types of energy. In the following, the conductivity of electricity is the value of interest.

#### Metals:

The conductivity of metals is based on the free electrons (so-called Fermi gas) due to the metal bonding. Already with low energy electrons become sufficiently detached from the atoms and a conductivity is achieved.

The conductivity depends, inter alia, on the temperature. If the temperature rises, the metal atoms swing ever stronger, so that the electrons are constrained in their movements. Consequence, the resistance increases. The best conductors, gold and silver, are used relatively rare because of the high costs (gold e.g. for the contacting of the finished chips). The alternatives in the semiconductor technology for the wiring of the individual components of microchips are aluminum and copper.

#### Salts:

In addition to metals, salts can also conduct electricity. There are no free electrons, so the conductivity depends on ions which can be solved when a salt is melting or dissolving, so that the ions are free to move (see chapter chemical bonds for details).

# Free electrons form an electron gas Al<sup>3+</sup> Al<sup>3+</sup> Al<sup>3+</sup> Al<sup>3+</sup> Al<sup>3+</sup> Al<sup>3+</sup> Al<sup>3+</sup> Al<sup>3+</sup> Fixed aluminum atoms

Fig. 1.9: Metallic bonding: fixed ions and free valence electrons (Fermi gas)

#### 1.5.2 Insulators

Insulators possess no free charge carriers and thus are non-conductive.

#### The atomic bond:

The atomic bond is based on shared electron pairs of nonmetals. The elements which behave like nonmetals have the desire to catch electrons, thus there are no free electrons which might serve as charge carriers.

#### The ionic bond:

In the solid state, ions are arranged in a grid network. By electrical forces, the particles are held together. There are no free charge carriers to enable a current flow. Thus substances composed of ions can be both conductor and insulator.

#### 1.5.3 Semiconductors

Semiconductors are solids whose conductivity lies between the conductivity of conductors and insulators. Due to exchange of electrons - to achieve the noble gas configuration - semiconductors arrange as lattice structure. Unlike metals, the conductivity increases with increasing temperature.

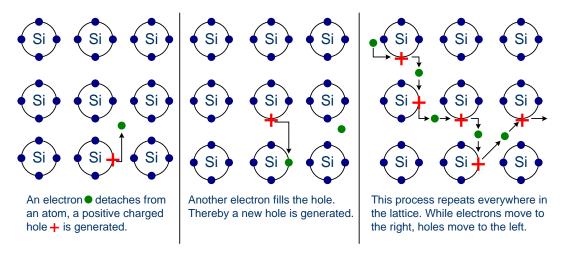

Increasing temperatures leads to broken bonds and free electrons are generated. At the location at which the electron was placed, a so-called defect electron ("hole") remains.

The electron flow is based on the conductivity properties of semiconductors. The electronic band structure illustrates why semiconductors behave like this.

Fig. 1.10: Cut-out of a silicon lattice

#### 1.5.4 The band model

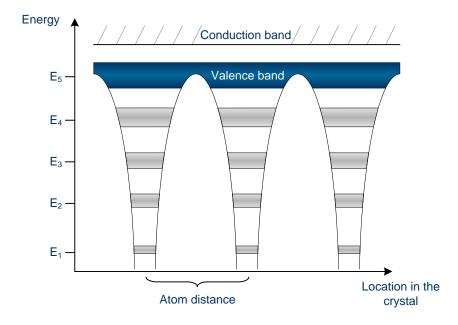

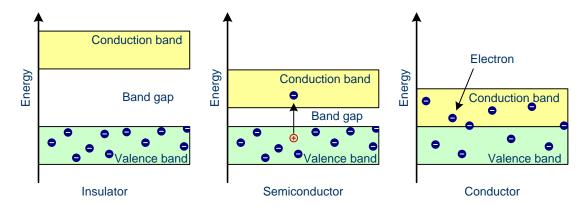

The electronic band structure is an energy schema to describe the conductivity of conductors, insulators, and semiconductors. The schema consists of two energy bands (valence and conduction band) and the band gap. The valence electrons - which serve as charge carriers - are located in the valence band, in the ground state the conduction band is occupied with no electrons. Between the two energy bands there is the band gap, its width affects the conductivity of materials.

#### The energy bands

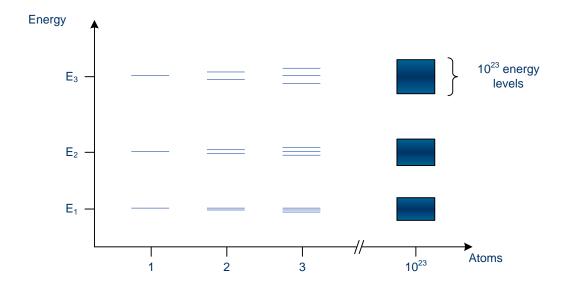

If we consider a single atom, there are according to the Bohr model of atoms sharply distinct energy levels, which may be occupied by electrons. If there are multiple atoms side by side they are interdependent, the discrete energy levels are fanned out. In a silicon crystal, there are approximately  $10^{23}$  atoms per cubic centimeter, so that the individual energy levels are no longer distinguishable from each other and thus form broad energy ranges.

The width of the energy bands depends on how strongly the electrons are bound to the atom. The valence electrons in the highest energy level interact strongly with those of neighboring atoms and can be solved relatively easily from an atom; with a very large number of atoms, a single electron can no longer be assigned to one single atom. As a result, the energy bands of the individual atoms merge to a continuous band, the valence band.

#### The band model of conductors

Fig. 1.11: Energy levels of atoms which are in interdependency with other atoms

Fig. 1.12: Energy bands of atoms which are in interdependency with other atoms

In conductors, the valence band is either not fully occupied with electrons, or the filled valence band overlaps with the empty conduction band. In general, both states occure at the same time, the electrons can therefore move inside the partially filled valence band or inside the two overlapping bands. In conductors there is no band gap between the valence band and conduction band.

#### The band model of insulators

In insulators the valence band is fully occupied with electrons due to the covalent bonds. The electrons can not move because they are "locked up" between the atoms. To achieve a conductivity, electrons from the valence band have to move into the conduction band. This prevents the band gap, which lies in-between the valence band and conduction band.

Only with considerable energy expenditure (if at all possible) the band gap can be overcome; thus leading to a negligible conductivity.

#### The band model of semiconductors

Even in semiconductors, there is a band gap, but compared to insulators it is so small that even at room temperature electrons from the valence band can be lifted into the conduction band. The electrons can move freely and act as charge carriers. In addition, each electron also leaves a hole in the valence band behind, which can be filled by other electrons in the valence band. Thus one gets wandering holes in the valence band, which can be viewed as positive charge carriers.

There are always pairs of electrons and holes, so that there are as many negative as positive charges, the semiconductor crystal as a whole is neutral. A pure undoped semiconductor is known as intrinsic semiconductor. Per cubic centimeter there are about  $10^{10}$  free electrons and holes (at room temperature).

Since the electrons always assume the energetically lowest state, they fall back into the valence band and recombine with the holes if there is no energy supply. At a certain temperature an equilibrium is arranged between the electrons elevated to the conduction band and the electrons falling back. With increasing temperature the number of electrons that can leap the band gap is increased, and thus increasing the conductivity of semiconductors.

Since the width of the band gap represents a certain energy corresponding to a particular wavelength, one tries to alter the width selective in order to obtain certain colors of light emitting diodes (LED). This may be achieved by combining different materials. Gallium arsenide (GaAs) has a band gap of 1.4 eV (electron volts, at room temperature) and thus emits red light.

The intrinsic conductivity of silicon is of no interest for the functioning of components, since it depends, inter alia, on the supplied energy. Which means that it changes with the temperature; in addition a conductivity comparable to metals is only possible at

Fig. 1.13: The band model

very high temperatures (several hundred degrees Celsius). In order to deliberately influence the conductivity of semiconductors, impurity atoms can be introduced into the regular silicon lattice to alter the number of free electrons and holes.

## 1.6 Doping: n- and p-semiconductors

#### 1.6.1 Doping

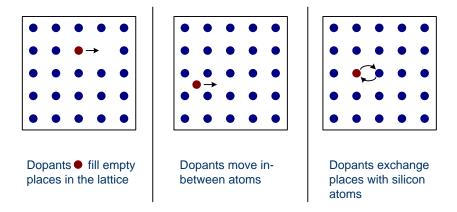

Doping means the introduction of impurities into a semiconductor crystal to the defined modification of conductivity. Two of the most important materials silicon can be doped with, are boron (3 valence electrons = 3-valent) and phosphorus (5 valence electrons = 5-valent). Other materials are aluminum, indium (3-valent) and arsenic, antimony (5-valent).

The dopant is integrated into the lattice structure of the semiconductor crystal, the number of outer electrons define the type of doping. Elements with 3 valence electrons are used for p-type doping, 5-valued elements for n-doping. The conductivity of a deliberately contaminated silicon crystal can be increased by a factor of  $10^6$ .

#### 1.6.2 n-doping

The 5-valent dopant has an outer electron more than the silicon atoms. Four outer electrons combine with ever one silicon atom, while the fifth electron is free to move and serves as charge carrier. This free electron requires much less energy to be lifted

from the valence band into the conduction band, than the electrons which cause the intrinsic conductivity of silicon. The dopant, which emits an electron, is known as an electron donor (donare, lat. = to give).

The dopants are positively charged by the loss of negative charge carriers and are built into the lattice, only the negative electrons can move. Doped semimetals whose conductivity is based on free (negative) electrons are n-type or n-doped. Due to the higher number of free electrons those are also named as majority charge carriers, while free mobile holes are named as the minority charge carriers.

Fig. 1.14: n-doping with phosphorus

Arsenic is used as an alternative to phosphorus, because its diffusion coefficient is lower. This means that the dopant diffusion during subsequent processes is less than that of phosphorus and thus the arsenic remains at the position where it was introduced into the lattice originally.

#### 1.6.3 p-doping

In contrast to the free electron due to doping with phosphorus, the 3-valent dopant effect is exactly the opposite. The 3-valent dopants can catch an additional outer electron, thus leaving a hole in the valence band of silicon atoms. Therefore the electrons in the valence band become mobile. The holes move in the opposite direction to the movement of the electrons. The necessary energy to lift an electron into the energy level of indium as a dopant, is only 1 % of the energy which is needed to raise a valence electron of silicon into the conduction band.

With the inclusion of an electron, the dopant is negatively charged, such dopants are called acceptors (acceptare, lat. = to add). Again, the dopant is fixed in the crystal lattice, only the positive charges can move. Due to positive holes these semiconductors

are called p-conductive or p-doped. Analog to n-doped semiconductors, the holes are the majority charge carriers, free electrons are the minority charge carriers.

Fig. 1.15: p-doping with boron

Doped semiconductors are electrically neutral. The terms n- and p-type doped do only refer to the majority charge carriers. Each positive or negative charge carrier belongs to a fixed negative or positive charged dopant.

N- and p-doped semiconductors behave approximately equal in relation to the current flow. With increasing amount of dopants, the number of charge carriers increases in the semiconductor crystal. Here it requires only a very small amount of dopants. Weakly doped silicon crystals contain only 1 impurity per 1,000,000,000 silicon atoms, high doped semiconductors for example contain 1 foreign atom per 1,000 silicon atoms.

#### 1.6.4 Electronic band structure in doped semiconductors

Through the introduction of a dopant with five outer electrons, in n-doped semiconductors there is an electron in the crystal which is not bound and therefore can be moved with relatively little energy into the conduction band. Thus in n-doped semiconductors one finds a donator energy level near the conduction band edge, the band gap to overcome is very small.

Analog, through introduction of a 3-valent dopant in a semiconductor, a hole is available, which may be already occupied at low-energy by an electron from the valence band of the silicon. For p-doped semiconductors one finds an acceptor energy level near the valence band.

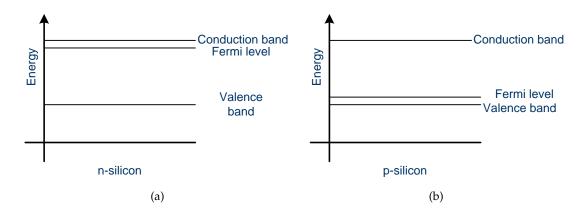

Fig. 1.16: Band model of p- and n-type doped semiconductors

### 1.7 The p-n junction

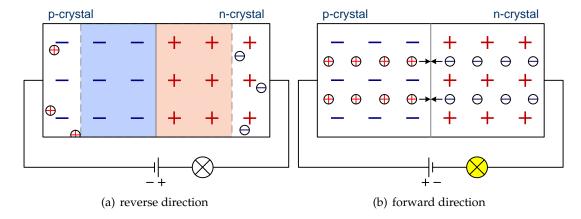

#### 1.7.1 p-n junction at thermal equilibrium

The p-n junction is the transition area between two n- and p-doped semiconductor crystals. In this area there are no free charge carriers, since the free electrons of the n-conductor, and the holes of the p-doped crystal in the vicinity of the interface recombine with each other, which means that the electrons fill the holes. This charge movement (diffusion) is obtained in consequence of a concentration gradient: since there is only a few number of electrons in the p-area and only a few number of holes in the n-region, the majority charge carriers (electrons in the n-crystal, holes in the p-crystal) move into the contrary doped semiconductor. The crystal lattice at the interface must not be interrupted, a simple "pressing together" of a p-type and a n-doped silicon crystal does not allow a functional p-n junction.

The regions near the interface are loaded due to the loss of free charge carriers (positive charge in the n-crystal, negative charge in the p-crystal). The more charge carriers recombine, the greater the depletion zone and thus the voltage difference of n- and p-crystal. With a certain amount of this potential gap, the recombination of holes and electrons comes to a complete standstill, the charge carriers can no longer overcome the electric field. In silicon this limit is at about 0.7 V.

A p-n junction represents an electrical component with the function to allow an electric current in one direction (called the forward biased condition) and to block the current

Fig. 1.17: p-n junction without an external applied voltage

in the opposite direction (the reverse biased condition): a diode.

#### 1.7.2 p-n junction with external applied voltage

If the n-type crystal is applied to a positive and the p-crystal to a negative voltage, the electric field inside the semiconductor and the field of the voltage source are in the same direction. Thus the electric field at the p-n junction is reinforced. The oppositely charged free carriers are attracted by the poles of the voltage source, thus the barrier layer is increased and a current flow is inhibited.

If the external voltage is applied in the reverse direction, the external and internal electric field are in the opposite direction and the inner filed is weakened. If the inner field is completely eliminated from the outer field, a constantly flow of free charge carriers from the power source to the interface is possible and the carriers can recombine continuously: there is electric current.

The diode can be used as a rectifier: to convert alternating current into direct current. Areas where p- and n-doped semiconductor crystals are in contact, are found in many electrical devices in the semiconductor technology.

Fig. 1.18: p-n junction with an external applied voltage

#### 1.8 Field-effect transistors

#### 1.8.1 General layout

A transistor is an electronic semiconductor device for switching or amplifying electricity. The current can flow through two junctions - called drain and source -, while the third (gate electrode) is used for control. In addition to the field-effect transistor (FET) which is described here, there is another basic transistor, the bipolar transistor. The operation of the bipolar transistor is based on charge carriers of both polarities (thus bipolar), holes and electrons. Field-effect transistors, also known as unipolar transistors, use either electrons or holes for the transport of electricity.

The transistor is the basic component in semiconductor manufacturing, in modern microchips there are found several millions to billions of transistors. Through the combination of multiple transistors, all logic gates can be implemented in order to obtain logic output signals of corresponding input signals. Thus transistors form the heart of every microprocessor, memory chip, etc. The transistor is the most abundant object made by mankind, and thus became indispensable in today's life.

The transistor is built up layer by layer. This article describes the basic structure of a simple field-effect transistor, the various possibilities to realize the miscellaneous layers will follow in the later chapters.

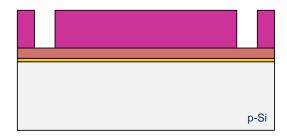

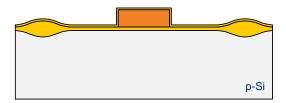

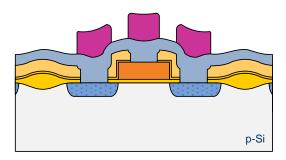

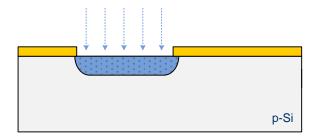

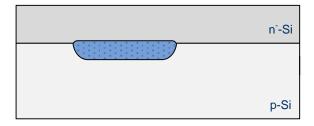

#### 1.8.2 Construction of a n-channel FET

| 1. Substrate: | Basis | for a | a n-channel | field-effect | transistor | is a | p-doped | (boron) | silicon |

|---------------|-------|-------|-------------|--------------|------------|------|---------|---------|---------|

| substrate.    |       |       |             |              |            |      |         |         |         |

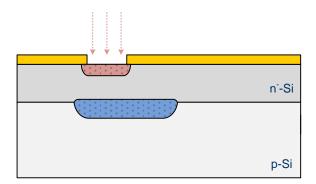

**2. Oxidation:** On top of the substrate, a thin layer of silicon dioxide  $SiO_2$  (the gate oxide) is created via thermal oxidation. It is used for insulation of the later deposited gate and the substrate.

**3. Deposition:** In a LPCVD process nitride is deposited, it is used later as an masking during the field oxidation.

**4. Photolithography:** On top of the nitride a photoresist is spun on, exposed and developed. Thus a structured coating layer is fabricated which serves as an etching mask.

**5. Etching:** Only at resist free sites nitride is removed using reactive ion etching.

**6. Resist removal:** Subsequent the resist mask is removed in a wet-chemical developer solution.

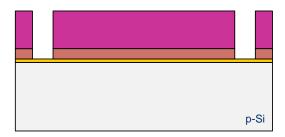

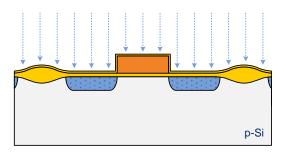

**7. Oxidation:** During field oxidation, the nitride serves as a mask layer, the thermal wet oxidation takes place only on the bare gate oxide. The grown field oxide is used for lateral isolation to adjacent devices.

**8. Etching:** Subsequent to the oxidation, the nitride is removed in a wet chemical etching process.

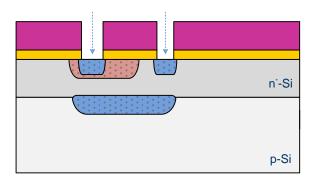

**9. Deposition:** Via low pressure CVD, polycrystalline silicon is deposited which represents the gate electrode.

**10. Photolithography:** Again a resist layer on top of the polysilicon is patterned.

**11. Etching:** The photoresist in turn serves as a mask layer, via reactive ion etching the gate is patterned.

12. Resist removal: The resist is removed via wet-chemical etching.

**13. Oxidation:** A thin oxide (post oxide) is deposited as an insulating layer for the gate electrode as well as a spacer for the subsequent source and drain implantation.

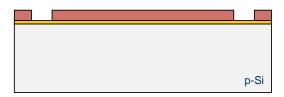

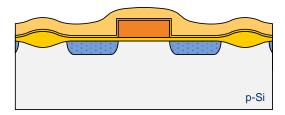

**14. Ion implantation:** Via ion implantation with phosphorus, the source and drain regions are introduced (n-type). Since the gate electrode acts as an mask during implantation, the width of the n-channel between the source and drain is preset. This is called self alignment.

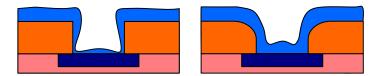

**15. Oxidation:** As an isolation a nonmetal is deposited (e.g. oxide). This happens in a LPCVD process with TEOS, which provides a good step coverage.

**16. Photolithography and etching:** In a further step a resist layer is structured and the edges of the contact holes are rounded in an isotropic etch process.

**17. Etching:** Subsequently the contact holes are opened in a highly anisotropic etch process.

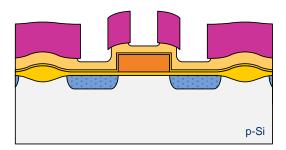

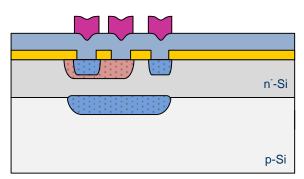

**18. Metallization:** The contact holes are filled with aluminum via sputtering.

19. Photolithography: In a final lithography step a new resist mask is patterned.

**20. Etching:** The pattern is transferred into the underlying metallization in an anisotropic dry etch process.

**21. Resist removal:** Finally, the resist is removed and aluminum conductors remain to actuate the transistor.

Actual the construction of a transistor is much more complex, since additional planarization layers for photolithography are necessary or secondary drain and source implantations have to be done to adjust the threshold voltage accurately. On the slopes of the gate elektrode additional (side wall) spacers can be formed to set the exact length of the channel or fine tune the doping profile respectively.

## 1.8.3 Mode of operation

#### **Enhancement-mode:**

Without a positive voltage applied to the gate there are no electrons available, which could act as free charge carriers between source and drain, since the substrate is p-doped. In steady state holes in the substrate act as majority charge carriers, while the electrons are minority charge carriers.

A positive voltage applied to the gate attracts electrons in the substrate, while holes are pushed away. Thus forming a conducting n-channel beneath the gate electrode and inbetween source and drain, respectively. The insulating silicon dioxide layer prevents a current flow between the substrate and the gate.

Since the transistor blocks the current flow without an applied voltage, the transistor is also called self-locking.

Fig. 1.19: Enhancement nFET

## Depletion-mode:

With a light n-type doping between the source and drain, a conductivity is even possible without a gate voltage (a voltage between source and drain is sufficient). So-called depletion FETs, or self-conducting transistors block the current flow only, if the voltage applied to the gate electrode is lower than the voltage at the source port. If the gate voltage is decreased, the electrons that are located beneath the gate, are pushed away the conductive electron-channel is lost.

# 1.9 Bipolar transistors

#### 1.9.1 General layout

The second important type of transistors, next to the field-effect transistor, is the bipolar transistor. Its mode of operation is based on both charge carriers (thus bipolar), electrons and holes. Bipolar transistors are faster than field-effect transistors, however, they require more space and are therefore more expensive in mass production.

Bipolar transistors consist essentially of two mutually connected p-n junctions with the layer sequence n-p-n or p-n-p. The connections of the bipolar transistor are emitter (E), base (B) and collector (C). While emitter and collector have the same doping, the very thin base layer in-between is doped contrarily.

In this article an NPN transistor in standard buried collector (SBC) construction is described, the mode of operation of PNP transistors is analog (the signs of the applied

voltages have just to be reversed).

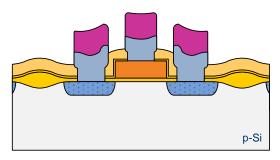

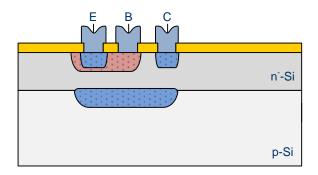

## 1.9.2 Construction of an NPN bipolar transistor

**1. Substrate:** Basis for an NPN bipolar transistor is a p-doped (boron) silicon substrate, a thick oxide layer (e.g. 600 nm) is deposited on top.

**2. Buried Layer Implantation:** The oxide serves as an implantation mask. As dopant antimony (Sb) is used, since its diffusion coefficient is lower than of phosphorus, and therefore the dopant won't diffuse as much in subsequent processes. The highly  $n^+$ -doped buried collector serves as a low-resistance contact surface for the collector port.

**3. Homoepitaxy:** In an epitactical process a high-impedance (low  $n^-$ -doped) collector layer is deposited (typically 10 microns).

**4. Base implantation:** With boron the p-doped base is introduced, a subsequent diffusion step magnifies its dimensions.

**5. Emitter and collector implantation:** With phosphorus both highly  $n^+$ -doped emitter and collector junctions are introduced.

**6. Metallization and photolithography:** Aluminum is deposited in a sputtering process for contacting and a resist layer is patterned on top of it.

**7. Etching:** Finally, the connectors for emitter, base, and collector are structured in an anisotropic dry etch process.

Due to many improvements, bipolar transistor do have more than three layers (npn or pnp). Nowadays the collector region consists out of at least two variable doped zones. The terms npn and pnp just describe the active area, not the actual filmstack.

## 1.9.3 Mode of operation

The two p-n junctions are hereinafter named as EB (emitter-base) and CB (collector-base). Without an external voltage a depletion zone forms at the interfaces of EB and CB. If a negative voltage is applied to the emitter and a positive voltage is applied to the collector, the depletion zone at EB decreases, while the depletion zone at CB increases. If a positive voltage is now applied to the base, EB becomes conductive - electrons can reach the base layer. As this layer is very thin, the charge carriers can be injected into the collector, where they are extracted due to the positive external voltage. Thus, a current flow from emitter to collector is established. Almost all electrons (>95 %) can reach the collector if only a small voltage is applied to the base, which means that with a relatively small base current (E to B) a very large collector current (E to C) is possible.

Fig. 1.20: SBC bipolar transistor

The two deep  $p^+$ -doped regions are used for lateral isolation from other components. In addition to the transistor a resistance (not in graphics) is needed, since bipolar transistors can not be controlled currentless.

## 1.10 Construction of a FinFET

## 1.10.1 General layout and mode of operation

The basic electrical layout and the mode of operation of a FinFET does not differ from a traditional field effect transistor. There is one source and one drain contact as well as a gate to control the current flow.

In contrast to planar MOSFETs the channel between source and drain is build as a three dimensional bar on top of the silicon substrate, called fin. The gate electrode is then wrapped around the channel, so that there can be formed several gate electrodes on each side which leads to reduced leakage effects and an enhanced drive current.

The manufacture of a bulk silicon-based multi gate transistor with three gates (tri gate) is described below.

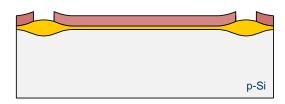

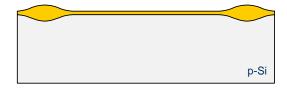

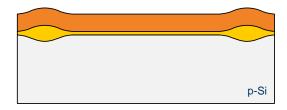

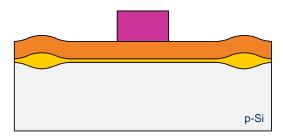

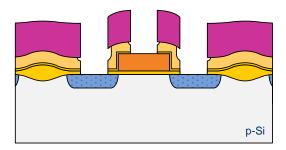

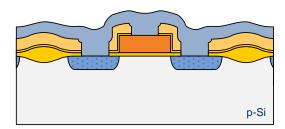

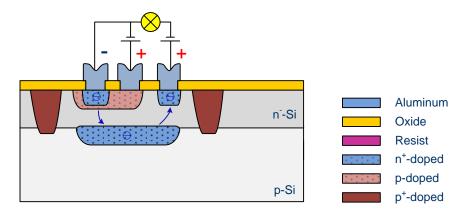

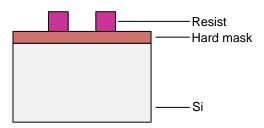

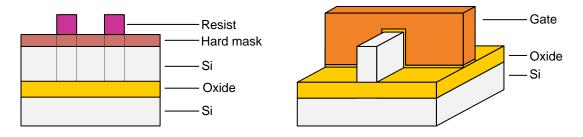

#### 1.10.2 Construction of a bulk silicon-based FinFET

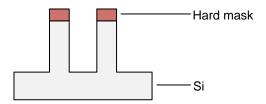

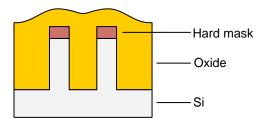

**1. Substrate:** Basis for a FinFET is a lightly p-doped substrate with a hard mask on top (e.g. silicon nitride) as well as a patterned resist layer.

**2. Fin etch:** The fins are formed in a highly anisotropic etch process. Since there is no stop layer on a bulk wafer as it is in SOI, the etch process has to be time based. In a 22 nm process the width of the fins might be 10 to 15 nm, the height would ideally be twice that or more.

Page 30

**3. Oxide deposition:** To isolate the fins from each other a oxide deposition with a high aspect ratio filling behavior is needed.

**4. Planarization:** The oxide is planarized by chemical mechanical polishing. The hard mask acts as a stop layer.

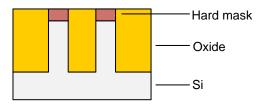

**5. Recess etch:** Another etch process is needed to recess the oxide film to form a lateral isolation of the fins.

**6. Gate oxide:** On top of the fins the gate oxide is deposited via thermal oxidation to isolate the channel from the gate electrode. Since the fins are still connected underneath the oxide, a high-dose angled implant at the base of the fin creates a dopant junction and completes the isolation (not illstrated).

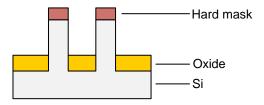

**7. Deposition of the gate:** Finally a highly  $n^+$ -doped poly silicon layer is deposited on top of the fins, thus up to three gates are wrapped around the channel: one on each side of the fin, and - depending on the thickness of the gate oxide on top - a third gate above.

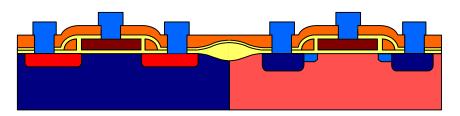

Fig. 1.21: FinFET in bulk process

The influence of the top gate can also be inhibited by the deposition of a nitride layer on top of the channel.

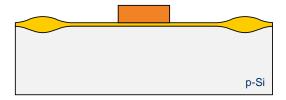

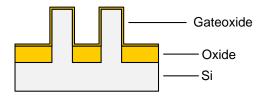

Since there is an oxide layer on an SOI wafer, the channels are isolated from each other anyway. In addition the etch process of the fins is simplified as the process can be stopped on the oxide easily.

Fig. 1.22: FinFET on SOI

# 2 Wafer fabrication

## 2.1 Properties of silicon

Silicon is the chemical element with the atomic number 14 in the periodic table of the elements. Silicon is a classic semiconductor, its conductivity lies between that of conductors and dielectrics. Naturally silicon (from the latin silex/silicis: pebbles) occurs only as oxide: silicon dioxide (SiO<sub>2</sub>) in form of sand, quartz, or silicate (compounds of silicon with oxygen, metals and others). Thus silicon is a very cheap starting material, whose value is determined with further processing. Other semiconductors such as germanium or gallium arsenide compound semiconductors offer substantially improved electrical properties than silicon: the charge carrier mobility and thus the resulting switching speeds are significantly higher in germanium and GaAs. However, silicon has significant advantages in contrast to other semiconductors.

On a silicon crystal oxide layers can be produced very easily, the resulting silicon dioxide is an insulator of highest quality which can be fabricated precisly on the substrate. To create similar insulators on germanium or gallium arsenide is very expensive. The possibility to change the conductivity by doping silicon is another big advantage. Other substances are in part very toxic, and compounds with these elements are not as durable and stable as in silicon. Requirement for the use of silicon in semiconductor manufacturing is that the silicon is present in an ultrapure form as single crystal. This means that the silicon atoms in the crystal lattice are regularly arranged and there are absolutely no undefined impurities in the material.

In addition to the single crystal, there is polysilicon (poly = many) and amorphous silicon (a-Si). While the single crystal silicon is the basis for microelectronics in form of circular wafers, the polycrystalline silicon is suitable to fulfill specific tasks (e.g. masking, gate electrode, ...). Polysilicon is made up of many individual irregularly arranged single crystals, and can be deposited and patterned very easily. Amorphous silicon does not have a regular but a disordered lattice structure and plays no role in semi-

Page 33

conductor manufacturing, but amorphous silicon offers advantages over other forms of silicon in the manufacture of thin film solar cells.

## 2.2 Raw silicon

#### 2.2.1 Production of raw silicon

Silicon as it is used in semiconductor manufacturing, is made up of quartz. Oxygen which reacts very fast with silicon even at room temperature, and which is present in quartz associated with silicon as silicon dioxide  ${\rm SiO_2}$ , must be removed. This is done just above the melting point of silicon (1414 °C) in furnaces using carbon. At 1460 °C oxygen cleaves of the silicon and reacts with carbon C to carbon monoxide CO:

$$SiO_2 + 2 CSi \longrightarrow 2 CO$$

Iron prevents the reaction of silicon and carbon to form silicon carbide. At these temperatures the carbon monoxide is in gaseous state and can be separated from the molten silicon easily. However, the raw silicon is still heavily polluted. There are up to 5 % impurities, such as for example iron, aluminum, phosphorus, and boron. These substances must be removed in additional processes.

## 2.2.2 Purification of the raw silicon

Using a trichlorosilane process many impurities are filtered out by distillation. The raw silicon and hydrogen chloride HCl react at about 300  $^{\circ}$ C to form gaseous hydrogen H<sub>2</sub> and trichlorosilane SiHCl<sub>3</sub>:

$$\mathrm{Si} + 3\,\mathrm{HCl} \longrightarrow \mathrm{SiHCl}_3 + \mathrm{H}_2$$

The contaminants which also react with the chlorine, need higher temperatures to transfer in the gaseous state. This allows separation of the trichlorosilane. Only car-

bon, phosphorus, and boron, which have similar condensation temperatures, can not be filtered out in this process.

The trichlorosilane process can be reversed, so that the purified silicon condeses in polycrystalline form. This is done at approximately 1100 °C by adding hydrogen inside a quartz chamber, in which thin silicon rods are placed:

$$\begin{split} \mathrm{SiHCl}_3 + \mathrm{H}_2 &\longrightarrow \mathrm{Si} + 3\,\mathrm{HCl} \\ &4\,\mathrm{SiHCl}_3 &\longrightarrow \mathrm{Si} + 3\,\mathrm{SiCl}_4 + 2\,\mathrm{H}_2 \end{split}$$

The silicon reflects on the silicon rods which grow to bars with a diameter of more than 30 mm. This polysilicon could already be transformed into a single crystal using the Czochralski process, however, the degree of purity for semiconductor manufacturing is still not high enough.

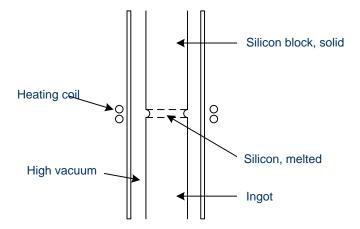

Fig. 2.1: Illustration of the zone cleaning process

## 2.2.3 Zone cleaning

To increase the purity once more a cleaning process is used. Thereby a high frequency coil is placed around the silicon rod to melt the silicon bars, and therefore the contaminations accumulate at the bottom due to higher solubility in the liquid phase; the surface tension of the silicon prevents the melt to flow out. By multiple repetition of this procedure, the content of impurities in silicon is further reduced and thus it can be

used for fabrication of the single crystal. To prevent further contamination, all of the processes are made under a vacuum atmosphere.

At the end of these processes the silicon has a purity of more than 99,9999999 %, which means that there is less than 1 foreign atom per 1 billion silicon atoms.

## 2.3 Fabrication of the single crystal

## 2.3.1 The single crystal

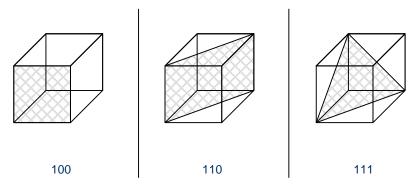

A single crystal (monocrystal), as it is required in semiconductor manufacturing, is a regular arrangement of atoms. There are polycrystalline (composition of many small single crystals) and amorphous silicon (disordered structure). Depending on the orientation of the lattice, silicon wafers have different surface structures which impact various properties as the charge carrier mobility or the behaviour in wet-chemical anisotropic etching of silicon.

Fig. 2.2: Crystal orientation

In micromechanics the crystal orientation is of particular importance. It allows microchannels with perpendicular walls on (110) silicon, whereas flank angles of  $54.74^{\circ}$  are possible on (100) orientation.

## 2.3.2 Czochralski process

The polycrystalline silicon, as it is present after the zone cleaning, is melted in a quartz crucible nearly above the melting point of silicon. Now dopants (e.g. boron or phos-

phorus) can be added to the melt to achieve appropriate electrical characteristics of the single crystal.

A seed crystal (a perfect single crystal) on a rotating rod is brought to the surface of the silicon melt. This seed crystal pretends the orientation of the silicon crystal. In contact with the seed crystal, the melt overtakes its crystal structure. The fact that the crucible temperature is only slightly above the melting point of silicon, the melt solidifies immediately on the seed and the crystal grows.

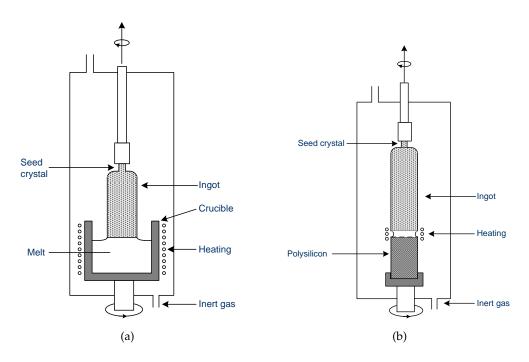

Fig. 2.3: Illustration of (a) the Czochralski and (b) the float-zone process

The seed is slowly pulled upward with constant rotation, while there is constant contact with the melt. The crucible turns in the opposite direction of the seed crystal. A constant temperature of the melt is essential to ensure a steady growth. The diameter of the single crystal is determined by the drawing speed, which provides 2 to 25 cm/h. The higher the drawing speed, the thinner the crystal. The entire apparatus is located in a controlled atmosphere, so that no oxidation of silicon can take place.

The disadvantage of this procedure is that the melt is accumulated with dopants during the process, since the dopants are more solubly in the melt than in the solid state. Thus the dopant concentration along the silicon rod is not constant. Also impurities or metals can dissolve from the crucible and built into the crystal.

Page 37

The advantages of this method are the lower costs, and the ability to produce larger wafer sizes as in flot-zone processes.

#### 2.3.3 Float-zone silicon

In contrast to the Czochralski process the polysilicon is not entirely molten, but, as in the zone cleaning, only a small area (a few millimeters).

Again, a seed crystal, which will be introduced to the end of the polycrystalline silicon rod, sets the crystal structure. The polycrystal is molten and assumes the structure of the seedling. The heated region is slowly guided along the rod, the polycrystalline silicon rod slowly transforms into a single crystal.

Since only a small portion of the polycrystalline silicon is molten, it can hardly be polluted (impurities accumulate at the bottom since their higher solubility). The doping is done by additions of dopants into the inert gas (eg with diborane or phosphine) which flows around the apparatus.

## 2.4 Wafer fabrication

## 2.4.1 Wafer separation and surface refinement

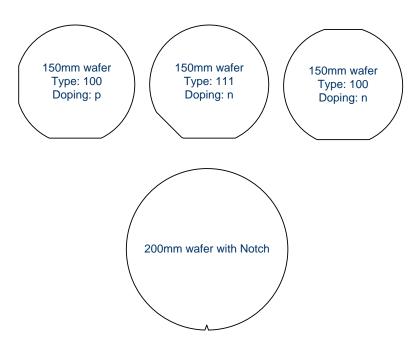

At first the single crystal is turned to a desired diameter and then bedight with one or two flats. The larger, first flat allows an precise alignment of the wafer during manufacturing. The second flat is used to detect the type of the wafer (crystal orientation, p-/n-type doped), but is not always used. Wafers with a diameter of 200 mm or above use a notch instead. This tiny notches on the edge of the disk also provide an alignment of the wafer, but take up much less costly wafer surface.

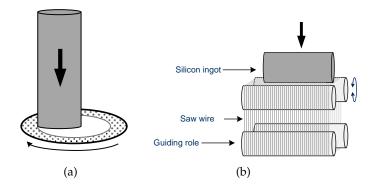

#### Sawing:

With an annular saw, whose cutting edge is filled with diamond splinters, the single crystal is sawn into thin discs = wafer. The saw provides a high accuracy during sawing without bumps. Up to 20 % of the crystal rod is lost due to the width of the saw blade. However, nowadays more often wire saws are used, in which multiple wafers can be cut at once from the staff. Therefore a long wire, which is wetted with a suspension of silicon carbide grains and a carrier (glycol or oil), is lead through rotating rollers. The

Fig. 2.4: Different types of wafers

silicon crystal is drained into the wire grid and thus cut into single wafers. The wire moves in counterstep with about 10 m/s and has a typically thickness of 0.1-0.2 mm.

Fig. 2.5: Annular and wire saw

After sawing, the slices have a rough surface, and due to mechanical stress damages in the crystal lattice. For finishing the surface, the wafers pass several process steps.

## Lapping:

Using granular abrasives (e.g. aluminum) 50 microns (0.05 mm) of the wafer surface are removed on a rotating steel disc. The grain size is reduced in stages, but the surface is re-injured due to the mechanical treatment. The flatness after lapping is about 2

microns.

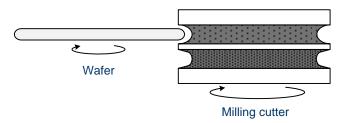

#### Beveling of the edge:

In subsequent processes, the discs must have no sharp edges, as deposited layers may flake off otherwise. Therfore the bevel of the wafers are rounded with a diamond cutter.

Fig. 2.6: Beveling

#### **Etching:**

In an additional wet etch process, with a mixture of hydrofluoric, acetic, and nitric acid, 50 microns are removed. Because this is a chemical process, the surface is not damaged. Crystal defects are permanently resolved.

#### **Polishing:**

This is the final step of surface refinement. At the end of the polishing step, the wafers do not have a bump of more than 3 nm (0.000003 mm). The wafers are treated with a mixture of sodium hydroxide NaOH, water, and silicon oxide grains. The oxide removes additional 5 microns from the surface, the hydroxide removes machining marks caused by the oxide grain.

## 2.4.2 Historical development of the wafer size

The manufacture of integrated circuits on silicon wafers started in the mid 1960s on wafers with a diameter of 25 mm. Nowadays, in modern semiconductor manufacturing wafers with a diameter of 150-300 mm are used. By 2012 the mass production of microchips on wafers with a diameter of 450 mm is expected; prototypes have already been produced for research purposes. The wafer surface is then increased by more than 300-fold of the tiny 1-inch wafer 50 years ago.

With larger wafers, the throughput rate increases significantly in the manufacture of microchips, whereby the cost is reduced accordingly in the production. Thus, with identical structure sizese more than twice as many chips can be produced on a 300 mm

| Type    | Diameter [mm] | Thickness [ $\mu$ m] | 1st flat [mm] | Bowing [ $\mu$ m] |

|---------|---------------|----------------------|---------------|-------------------|

| 6 inch  | $150 \pm 0.5$ | ≈700                 | 55-60         | 25                |

| 8 inch  | $200\pm0.5$   | ≈700                 | 55-60         | 25                |

| 12 inch | $300 \pm 0.5$ | ≈700                 | 55-60         | 25                |

Tab. 2.1: Typical data of wafers

wafer as on a 200 mm wafer. In addition, with increasing diameter the wafer's edge is less curved and thus the cut-off minimized (since chips are off rectangular shape).

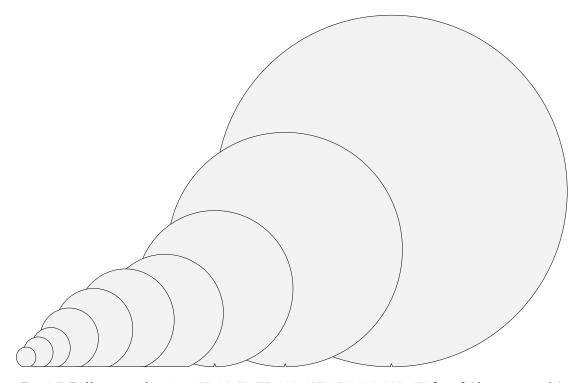

Fig. 2.7: Different wafer sizes: 25, 38, 51, 75, 100, 125, 150, 200, 300, 450 [mm] (drawn to scale)

# 2.5 Doping techniques